# MC68302

## Integrated Multiprotocol Processor User's Manual

For More Information On This Product, Go to: www.freescale.com

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

## PREFACE

The complete documentation package for the MC68302 consists of the M68000PM/AD, *MC68000 Family Programmer's Reference Manual*, MC68302UM/AD, *MC68302 Integrated Multiprotocol Processor User's Manual*, and the MC68302/D, *MC68302 Integrated Multiprotocol Processor Product Brief*.

The *MC68302 Integrated Multiprotocol Processor User's Manual* describes the programming, capabilities, registers, and operation of the MC68302; the *MC68000 Family Programmer's Reference Manual* provides instruction details for the MC68302; and the *MC68302 Low Power Integrated Multiprotocol Processor Product Brief* provides a brief description of the MC68302 capabilities.

This user's manual is organized as follows:

- Section 1 General Description

- Section 2 MC68000/MC68008 Core

- Section 3 System Integration Block (SIB)

- Section 4 Communications Processor (CP)

- Section 5 Signal Description

- Section 6 Electrical Characteristics

- Section 7 Mechanical Data And Ordering Information

- Appendix B Development Tools and Support

- Appendix C RISC Microcode from RAM

- Appendix D MC68302 Applications

- Appendix E SCC Programming Reference

- Appendix F Design Checklist

## **ELECTRONIC SUPPORT:**

The Technical Support BBS, known as AESOP (Application Engineering Support Through On-Line Productivity), can be reach by modem or the internet. AESOP provides commonly asked application questons, latest device errata, device specs, software code, and many other useful support functions.

Modem: Call 1-800-843-3451 (outside US or Canada 512-891-3650) on a modem that runs at 14,400 bps or slower. Set your software to N/8/1/F emulating a vt100.

Internet: This access is provided by telneting to pirs.aus.sps.mot.com [129.38.233.1] or through the World Wide Web at http://pirs.aus.sps.mot.com.

## - Sales Offices -

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

#### **UNITED STATES**

| ALABAMA, Huntsville<br>ARIZONA, Tempe<br>CALIFORNIA, Agoura Hills<br>CALIFORNIA, Los Angeles<br>CALIFORNIA, Irvine<br>CALIFORNIA, RosevIlle<br>CALIFORNIA, San Diego<br>CALIFORNIA, Sunnyvale<br>COLORADO, Colorado Springs<br>COLORADO, Colorado Springs<br>COLORADO, Denver<br>CONNECTICUT, Wallingford<br>FLORIDA, Maitland<br>FLORIDA, Pompano Beach/<br>Fort Lauderdal<br>FLORIDA, Clearwater<br>GEORGIA, Atlanta<br>IDAHO, Boise<br>ILLINOIS, Chicago/Hoffman Estates<br>INDIANA, Fort Wayne<br>INDIANA, Fort Wayne<br>INDIANA, Kokomo<br>IOWA, Cedar Rapids<br>KANSAS, Kansas City/Mission<br>MARYLAND, Columbia | (205) 464-6800<br>(602) 897-5056<br>(818) 706-1929<br>(310) 417-8848<br>(714) 753-7360<br>(916) 922-7152<br>(619) 541-2163<br>(408) 749-0510<br>(719) 599-7497<br>(303) 337-3434<br>(203) 949-4100<br>(407) 628-2636<br>(305) 486-9776<br>(813) 538-7750<br>(404) 729-7100<br>(208) 323-9413<br>(708) 490-9500<br>(219) 436-5818<br>(317) 571-0400<br>(317) 457-6634<br>(319) 373-1328<br>(913) 451-8555<br>(410) 381-1570 | MASSACHUSETTS, Marborough<br>MASSACHUSETTS, Woburn<br>MICHIGAN, Detroit<br>MINNESOTA, Minnetonka<br>MISSOURI, St. Louis<br>NEW JERSEY, Fairfield<br>NEW YORK, Fairport<br>NEW YORK, Hauppauge<br>NEW YORK, Poughkeepsie/Fishkill<br>NORTH CAROLINA, Raleigh<br>OHIO, Cleveland<br>OHIO, Cleveland<br>OHIO, Cleveland<br>OHIO, Columbus Worthington<br>OHIO, Dayton<br>OKLAHOMA, Tulsa<br>OREGON, Portland<br>PENNSYLVANIA, Colmar<br>Philadelphia/Horsham<br>TENNESSEE, Knoxville<br>TEXAS, Austin<br>TEXAS, Austin<br>TEXAS, Houston<br>TEXAS, Plano<br>VIRGINIA, Richmond<br>WASHINGTON, Bellevue<br>Seattle Access<br>WISCONSIN, Milwaukee/Brookfield | (200) 022-9900                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| CANADA<br>BRITISH COLUMBIA, Vancouver<br>ONTARIO, Toronto<br>ONTARIO, Ottawa<br>QUEBEC, Montreal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (604) 293-7605<br>(416) 497-8181<br>(613) 226-3491<br>(514) 731-6881                                                                                                                                                                                                                                                                                                                                                       | MALAYSIA, Penang<br>MEXICO, Mexico City<br>MEXICO, Guadalajara<br>Marketing<br>Customer Service<br>NETHERLANDS, Best<br>PUERTO RICO, San Juan<br>SINGAPORE<br>SPAIN, Madrid<br>or<br>SWEDEN, Solpa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60(4)374514<br>52(5)282-2864<br>52(36)21-8977<br>52(36)21-9023<br>52(36)669-9160<br>(31)49988 612 11 |

| INTERNATIONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                            | PUERTO RICO, San Juan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (809)793-2170                                                                                        |

| AUSTRALIA, Melbourne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (61-3)887-0711                                                                                                                                                                                                                                                                                                                                                                                                             | SINGAPORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (65)2945438                                                                                          |

| AUSTRALIA, Sydney<br>BRAZIL, Sao Paulo<br>CHINA, Beijing<br>FINLAND, Helsinki                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (61(2)906-3855<br>55(11)815-4200                                                                                                                                                                                                                                                                                                                                                                                           | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34(1)457-8204<br>34(1)457-8254                                                                       |

| CHINA, Beijing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86 505-2180                                                                                                                                                                                                                                                                                                                                                                                                                | SWEDEN, Solna<br>SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei<br>THAU AND, Bangkok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46(8)734-8800                                                                                        |

| FINLAND, Helsinki                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 358-0-35161191                                                                                                                                                                                                                                                                                                                                                                                                             | SWITZERLAND, Geneva                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41(22)7991111                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 358(49)211501                                                                                                                                                                                                                                                                                                                                                                                                              | SWITZERLAND, Zurich                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41(1)730 4074<br>886(2)717-7089                                                                      |

| FRANCE, Paris/Vanves<br>GERMANY, Langenhagen/ Hanover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33(1)40 955 900<br>49(511)789911                                                                                                                                                                                                                                                                                                                                                                                           | THAILAND. Bangkok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (66-2)254-4910                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 00 00100 0                                                                                                                                                                                                                                                                                                                                                                                                              | THAILAND, Bangkok<br>UNITED KINGDOM, Aylesbury                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44(296)395-252                                                                                       |

| GERMANY, Nuremberg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49 911 64-3044                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |

| GERMANY, Munich<br>GERMANY, Nuremberg<br>GERMANY, Sindelfingen<br>GERMANY,Wiesbaden<br>HONG KONG, Kwai Fong<br>Tai Do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49 7031 69 910<br>49 611 761921                                                                                                                                                                                                                                                                                                                                                                                            | FULL LINE REPRESENT<br>COLORADO, Grand Junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ATIVES                                                                                               |

| HONG KONG, Kwai Fong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 852-4808333                                                                                                                                                                                                                                                                                                                                                                                                                | Cheryl Lee Whitely                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (303) 243-9658                                                                                       |

| TAIFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 002-00000000                                                                                                                                                                                                                                                                                                                                                                                                               | KANŠAS, Wichita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |

| INDIA, Bangalore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (91-812)627094                                                                                                                                                                                                                                                                                                                                                                                                             | Melinda Shores/Kelly Greiving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (316) 838 0190                                                                                       |

| ISRAEL, Tel Aviv<br>ITALY, Milan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 972(3)753-8222<br>39(2)82201                                                                                                                                                                                                                                                                                                                                                                                               | NEVADA, Reno<br>Galena Technology Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (702) 746 0642                                                                                       |

| JAPAN, Aizu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81(241)272231                                                                                                                                                                                                                                                                                                                                                                                                              | <b>NEW MEXICO</b> , Albuquerque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (102) 1 10 00 12                                                                                     |

| JAPAN, Atsugi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81(0462)23-0761                                                                                                                                                                                                                                                                                                                                                                                                            | S&S Technologies, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (505) 298-7177                                                                                       |

| JAPAN, Kumagaya                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81(0485)26-2600                                                                                                                                                                                                                                                                                                                                                                                                            | UTAH, Salt Lake City                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (901) 561 5000                                                                                       |

| JAPAN, Kyushu<br>JAPAN, Mito                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81(092)771-4212<br>81(0292)26-2340                                                                                                                                                                                                                                                                                                                                                                                         | Utah Component Sales, Inc.<br>WASHINGTON, Spokane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (801) 561-5099                                                                                       |

| JAPAN, Nagoya                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 01(0202)20 2040                                                                                                                                                                                                                                                                                                                                                                                                            | Doug Kenley                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (509) 924-2322                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81(052)232-1621                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |

| JAPAN, Osaka                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81(06)305-1801                                                                                                                                                                                                                                                                                                                                                                                                             | ARGENTINA, Buenos Aires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (E 44) 040 4707                                                                                      |

| JAPAN, Sendai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81(06)305-1801<br>81(22)268-4333                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (541) 343-1787                                                                                       |

| JAPAN, Sendai<br>JAPAN, Tachikawa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81(06)305-1801<br>81(22)268-4333<br>81(0425)23-6700                                                                                                                                                                                                                                                                                                                                                                        | ARGENTINA, Buenos Aires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |

| JAPAN, Sendai<br>JAPAN, Tachikawa<br>JAPAN, Tokyo<br>JAPAN, Yokohama                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81(06)305-1801<br>81(22)268-4333<br>81(0425)23-6700<br>81(03)3440-3311<br>81(045)472-2751                                                                                                                                                                                                                                                                                                                                  | ARGENTINA, Buenos Aires<br>Argonics, S.A.<br>HYBRID COMPONENTS RE<br>Elmo Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SELLERS<br>(818) 768-7400                                                                            |

| JAPAN, Sendai<br>JAPAN, Tachikawa<br>JAPAN, Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81(06)305-1801<br>81(22)268-4333<br>81(0425)23-6700<br>81(03)3440-3311                                                                                                                                                                                                                                                                                                                                                     | ARGENTINA, Buenos Aires<br>Argonics, S.A.<br>HYBRID COMPONENTS RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SELLERS                                                                                              |

## **TABLE OF CONTENTS**

#### Paragraph Number

#### Title

Page Number

#### Section 1 General Description

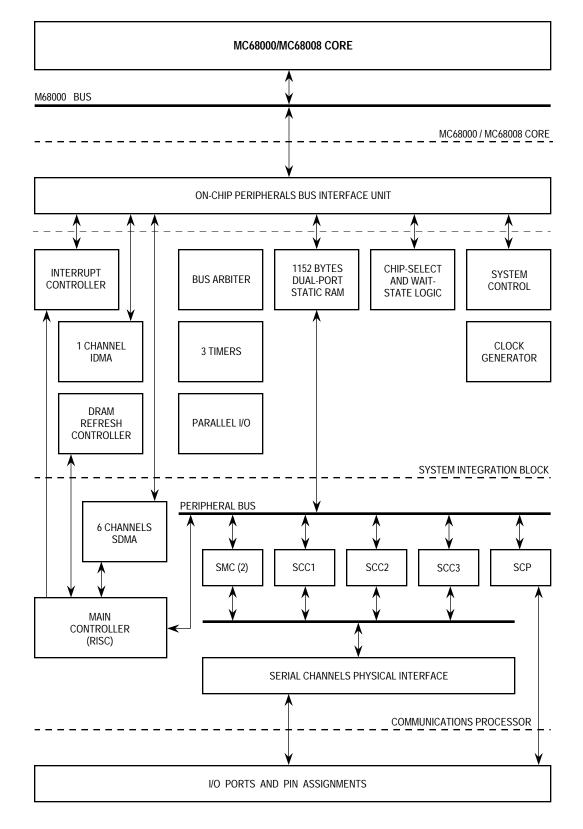

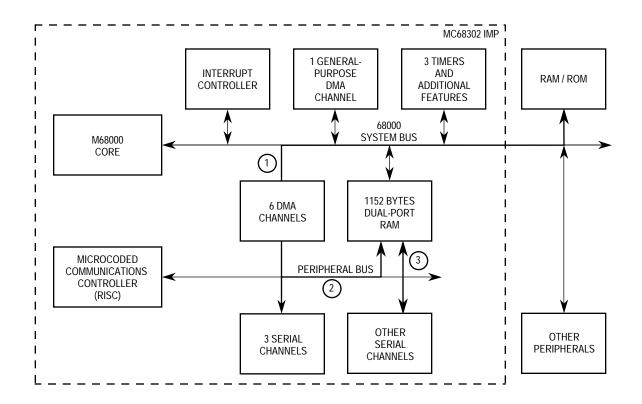

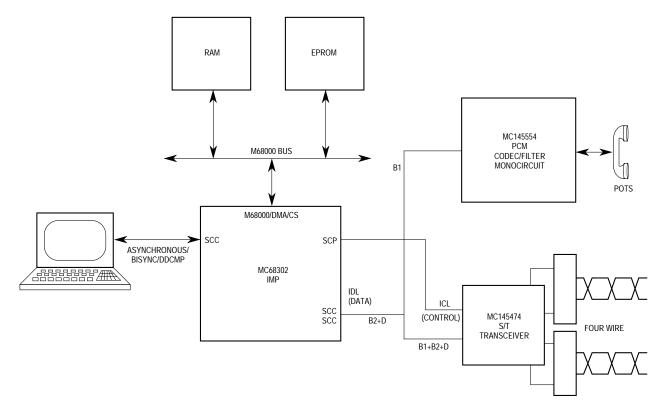

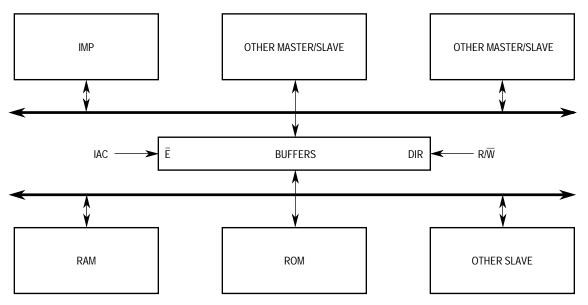

| 1.1 | Block Diagram                                  | 1-1 |

|-----|------------------------------------------------|-----|

| 1.2 | Features                                       | 1-3 |

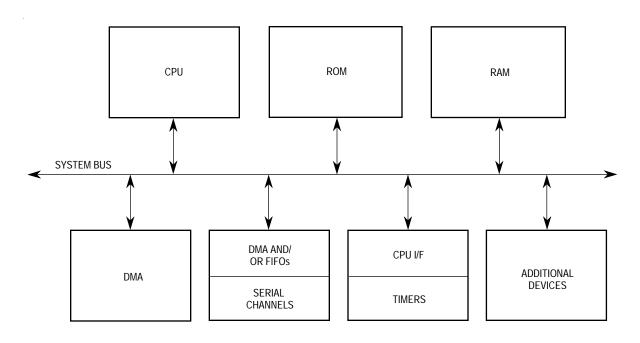

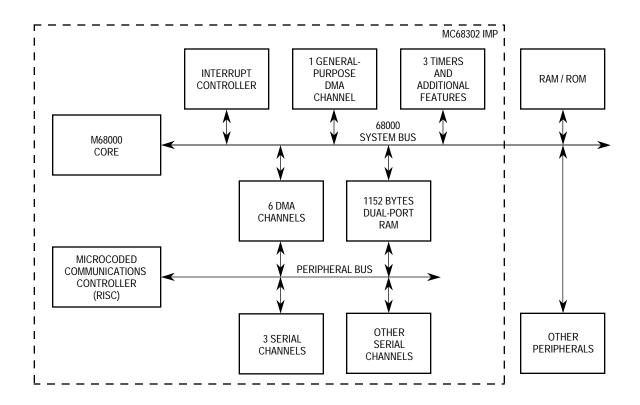

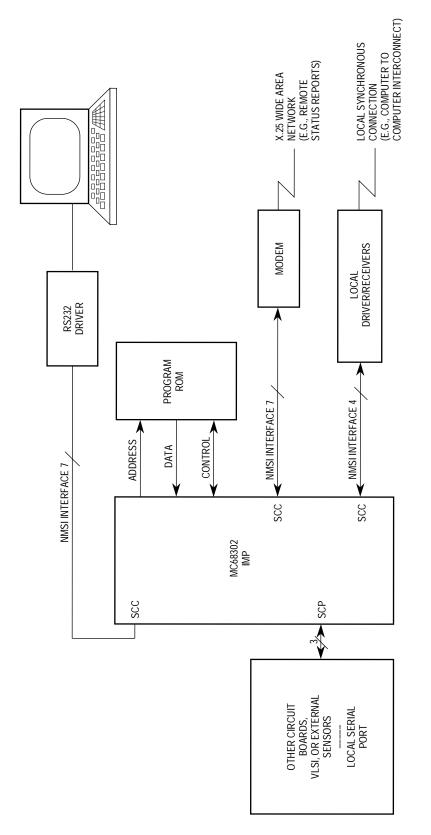

| 1.3 | MC68302 System Architecture                    | 1-4 |

| 1.4 | NMSI Communications-Oriented Environment       |     |

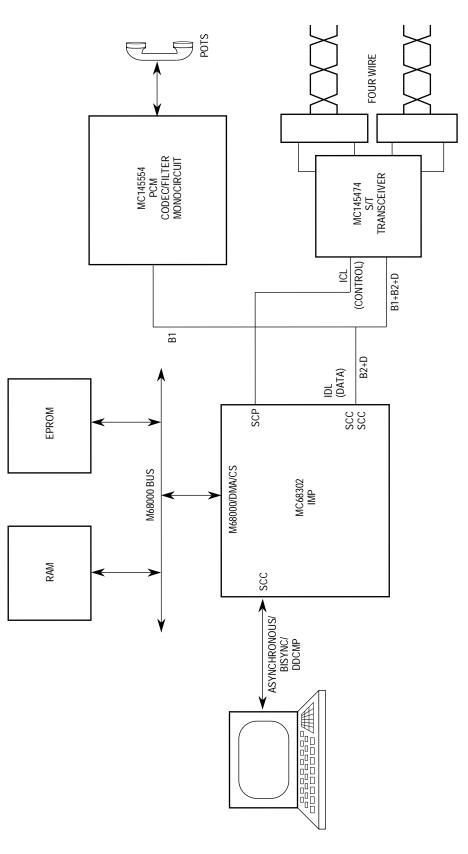

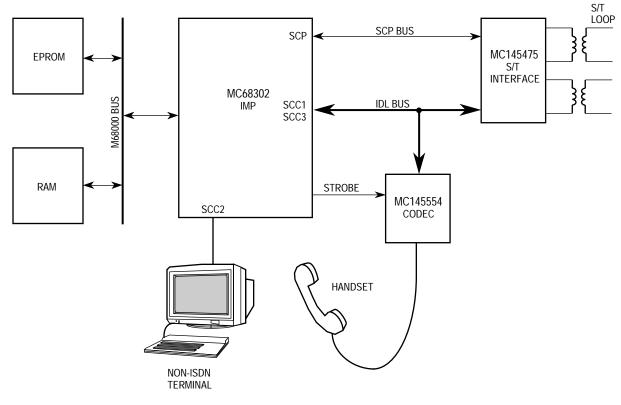

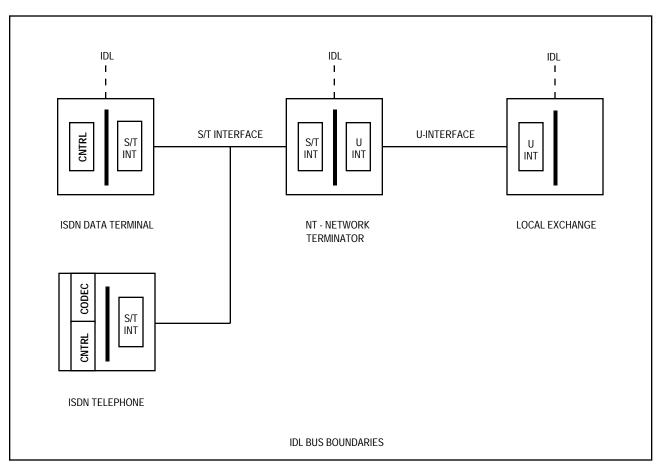

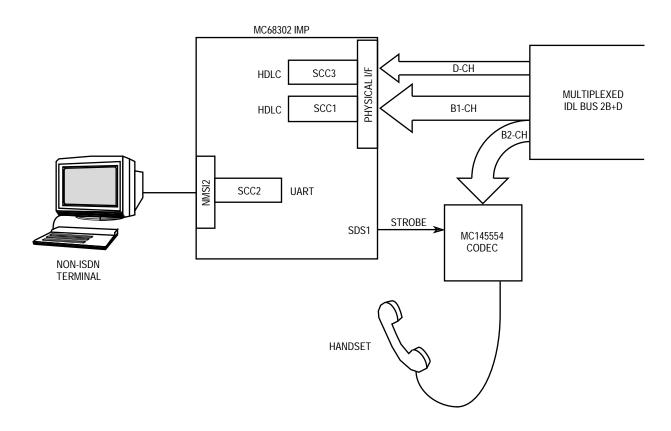

| 1.5 | Basic Rate ISDN or Digital Voice/Data Terminal | 1-6 |

#### Section 2 MC68000/MC68008 Core

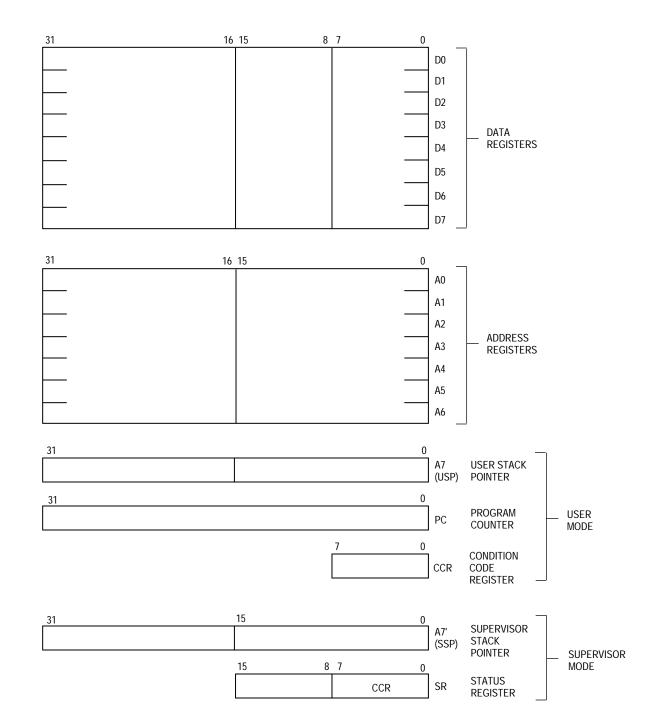

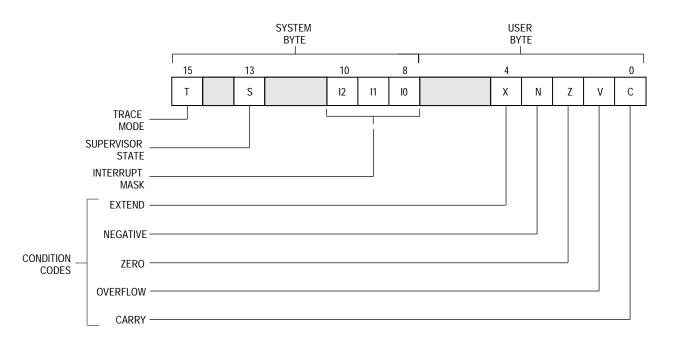

| 2.1   | Programming Model                 | 2-1 |

|-------|-----------------------------------|-----|

| 2.2   | Instruction Set Summary           |     |

| 2.3   | Address Spaces                    |     |

| 2.4   | Exception Processing              |     |

| 2.4.1 | Exception Vectors                 |     |

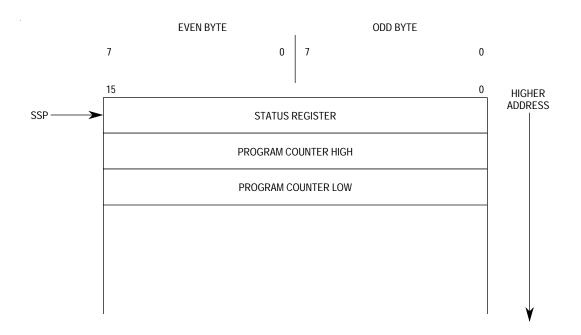

| 2.4.2 | Exception Stacking Order          |     |

| 2.5   | Interrupt Processing              |     |

| 2.6   | M68000 Signal Differences         |     |

| 2.7   | MC68302 IMP Configuration Control |     |

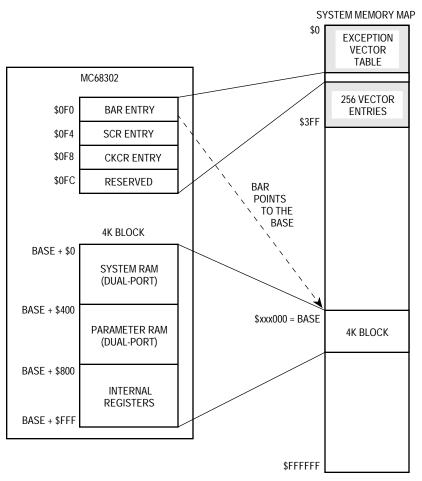

| 2.8   | MC68302 Memory Map                |     |

| 2.9   | Event Registers                   |     |

|       |                                   |     |

#### Section 3 System Integration Block (SIB)

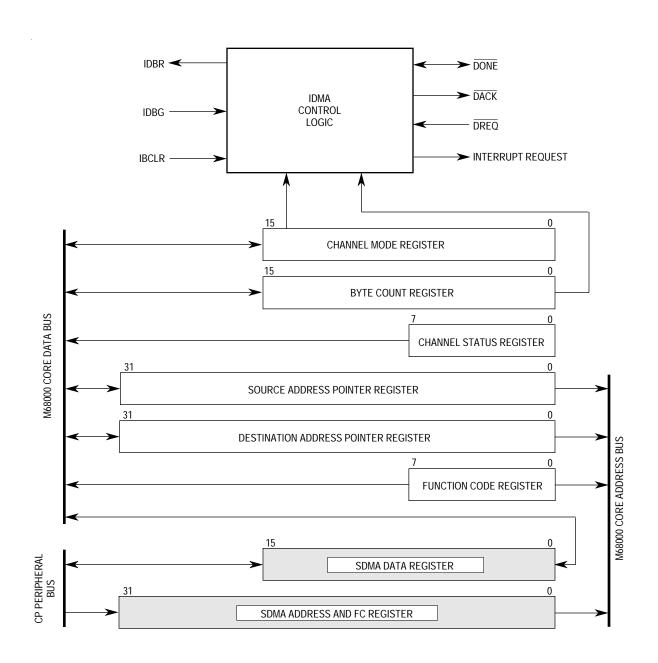

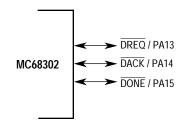

| 3.1     | DMA Control                                 |  |

|---------|---------------------------------------------|--|

| 3.1.1   | Key Features                                |  |

| 3.1.2   | IDMA Registers (Independent DMA Controller) |  |

| 3.1.2.1 | Channel Mode Register (CMR)                 |  |

| 3.1.2.2 | Source Address Pointer Register (SAPR)      |  |

| 3.1.2.3 | Destination Address Pointer Register (DAPR) |  |

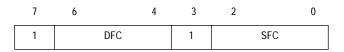

| 3.1.2.4 | Function Code Register (FCR)                |  |

| 3.1.2.5 | Byte Count Register (BCR)                   |  |

| 3.1.2.6 | Channel Status Register (CSR)               |  |

| 3.1.3   | Interface Signals                           |  |

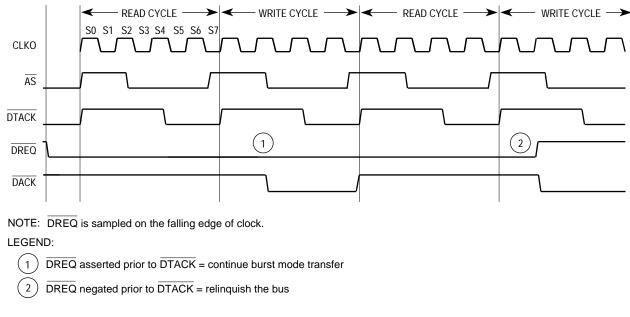

| 3.1.3.1 | DREQ and DACK                               |  |

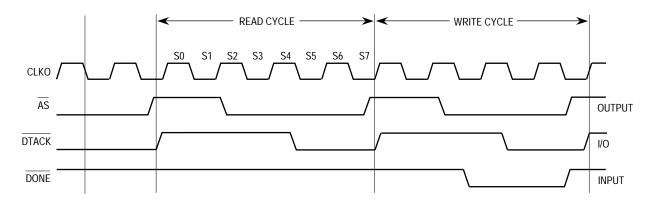

| 3.1.3.2 | DONE                                        |  |

| 3.1.4   | IDMA Operational Description                |  |

| 3.1.4.1 | Channel Initialization                      |  |

| 3.1.4.2 | Data Transfer                               |  |

|         |                                             |  |

| Paragraph<br>Number | Title                                  | Page<br>Number |

|---------------------|----------------------------------------|----------------|

| 3.1.4.3             | Address Sequencing                     | 3-10           |

| 3.1.4.4             | Transfer Request Generation            |                |

| 3.1.4.5             | Block Transfer Termination             | 3-12           |

| 3.1.5               | IDMA Programming                       | 3-13           |

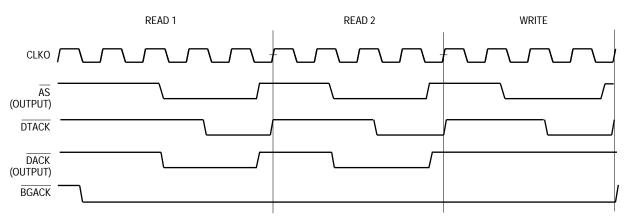

| 3.1.6               | DMA Bus Arbitration                    | 3-14           |

| 3.1.7               | Bus Exceptions                         | 3-14           |

| 3.1.7.1             | Reset                                  | 3-15           |

| 3.1.7.2             | Bus Error                              | 3-15           |

| 3.1.7.3             | Halt                                   | 3-15           |

| 3.1.7.4             | Relinquish and Retry                   | 3-15           |

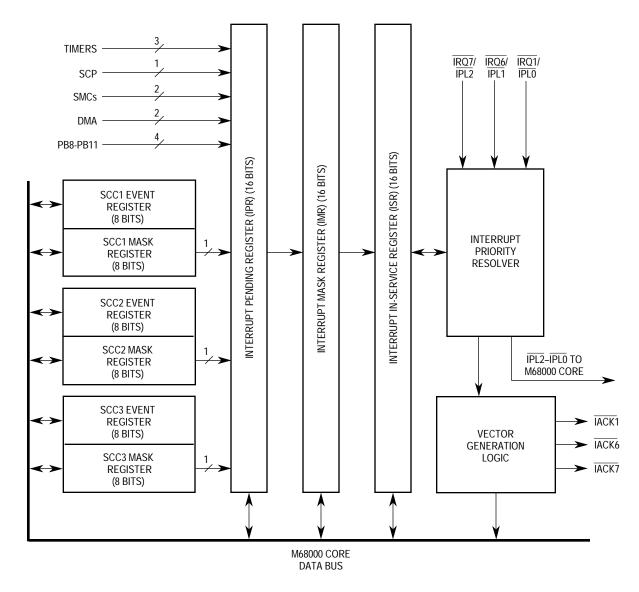

| 3.2                 | Interrupt Controller                   | 3-15           |

| 3.2.1               | Overview                               |                |

| 3.2.1.1             | IMP Interrupt Processing Overview      |                |

| 3.2.1.2             | Interrupt Controller Overview          |                |

| 3.2.2               | Interrupt Priorities                   |                |

| 3.2.2.1             | INRQ and EXRQ Priority Levels          |                |

| 3.2.2.2             | INRQ Interrupt Source Priorities       | 3-19           |

| 3.2.2.3             | Nested Interrupts                      |                |

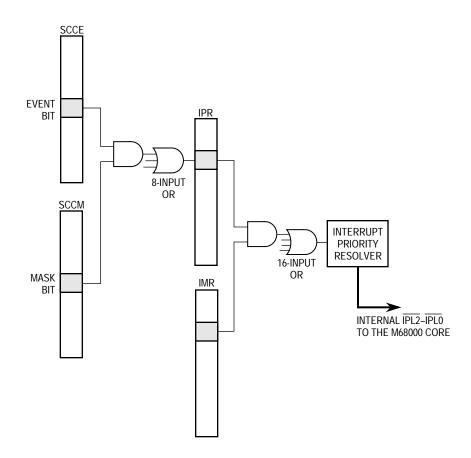

| 3.2.3               | Masking Interrupt Sources and Events   |                |

| 3.2.4               | Interrupt Vector                       |                |

| 3.2.5               | Interrupt Controller Programming Model |                |

| 3.2.5.1             | Global Interrupt Mode Register (GIMR)  |                |

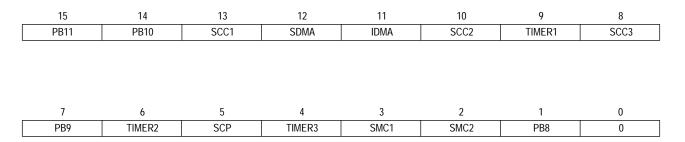

| 3.2.5.2             | Interrupt Pending Register (IPR)       |                |

| 3.2.5.3             | Interrupt Mask Register (IMR)          |                |

| 3.2.5.4             | Interrupt In-Service Register (ISR)    |                |

| 3.2.6               | Interrupt Handler Examples             |                |

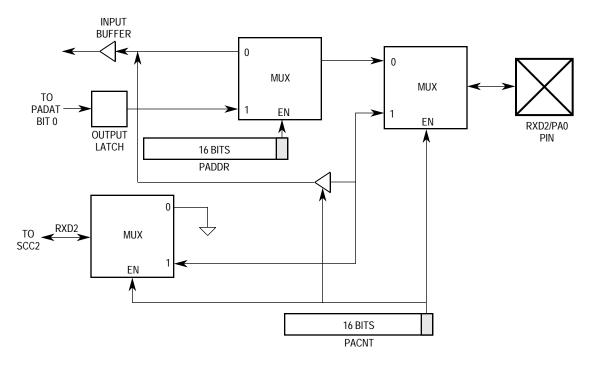

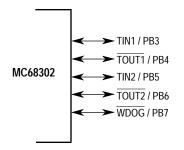

| 3.3                 | Parallel I/O Ports                     | 3-29           |

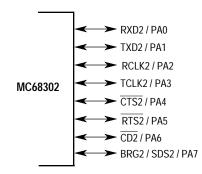

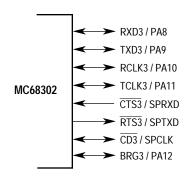

| 3.3.1               | Port A                                 | 3-29           |

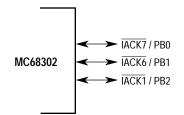

| 3.3.2               | Port B                                 |                |

| 3.3.2.1             | PB7–PB0                                |                |

| 3.3.2.2             | PB11–PB8                               | 3-32           |

| 3.3.3               | I/O Port Registers                     | 3-32           |

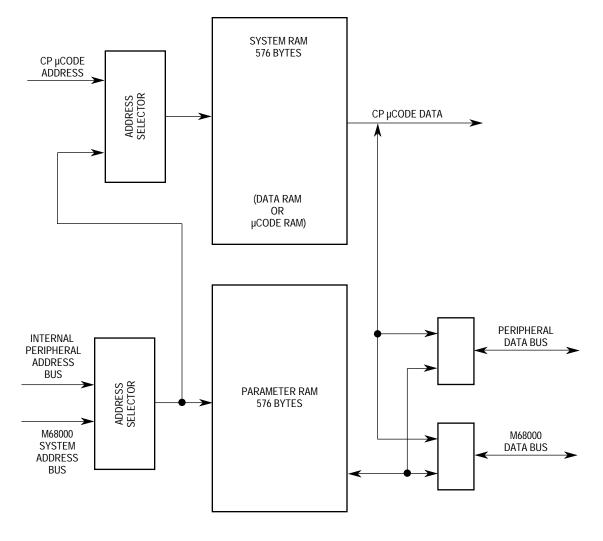

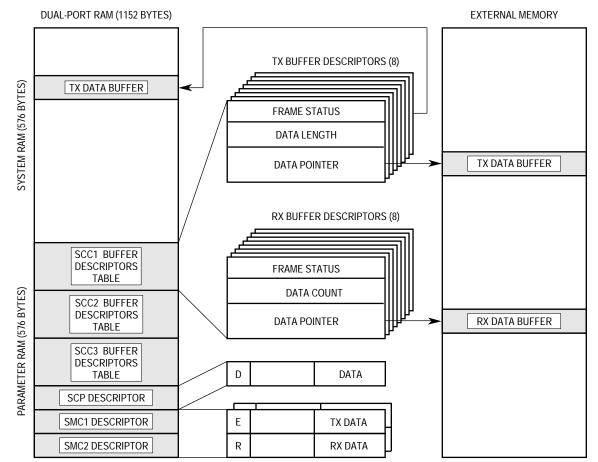

| 3.4                 | Dual-Port RAM                          |                |

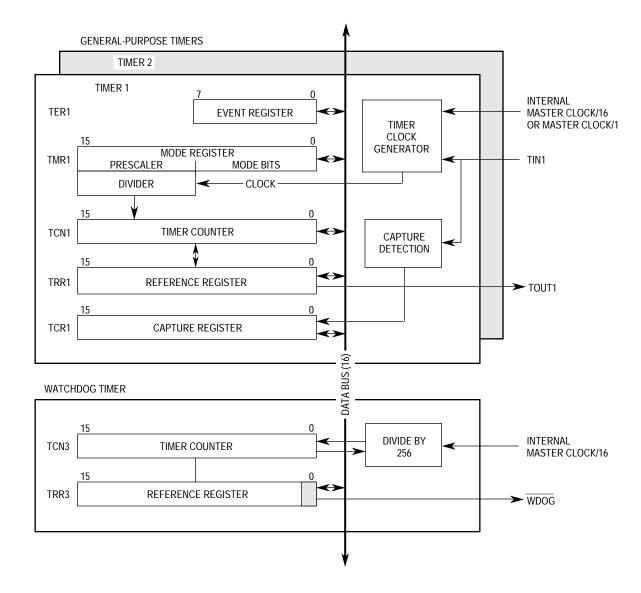

| 3.5                 | Timers                                 |                |

| 3.5.1               | Timer Key Features                     |                |

| 3.5.2               | General Purpose Timer Units            |                |

| 3.5.2.1             | Timer Mode Register (TMR1, TMR2)       |                |

| 3.5.2.2             | Timer Reference Registers (TRR1, TRR2) |                |

| 3.5.2.3             | Timer Capture Registers (TCR1, TCR2)   |                |

| 3.5.2.4             | Timer Counter (TCN1, TCN2)             | 3-39           |

| 3.5.2.5             | Timer Event Registers (TER1, TER2)     |                |

| 3.5.2.6             | General Purpose Timer Example          | 3-40           |

| 3.5.2.6.1           | Timer Example 1                        |                |

| 3.5.2.6.2           | Timer Example 2                        |                |

| 3.5.3               | Timer 3 - Software Watchdog Timer      | 3-41           |

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 3.5.3.1             | Software Watchdog Timer Operation                 | 3-41           |

| 3.5.3.2             | Software Watchdog Reference Register (WRR)        | 3-41           |

| 3.5.3.3             | Software Watchdog Counter (WCN)                   | 3-42           |

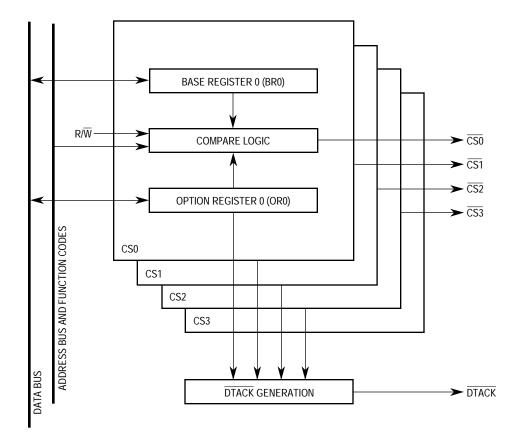

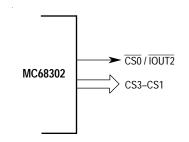

| 3.6                 | External Chip-Select Signals and Wait-State Logic |                |

| 3.6.1               | Chip-Select Logic Key Features                    |                |

| 3.6.2               | Chip-Select Registers                             | 3-45           |

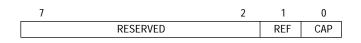

| 3.6.2.1             | Base Register (BR3–BR0)                           | 3-45           |

| 3.6.2.2             | Option Registers (OR3–OR0)                        |                |

| 3.6.3               | Chip Select Example                               | 3-48           |

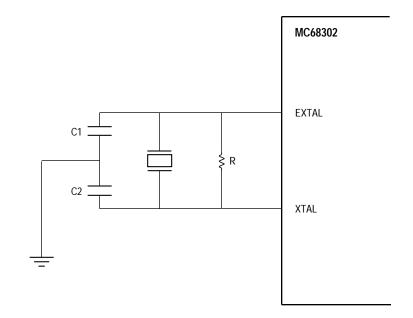

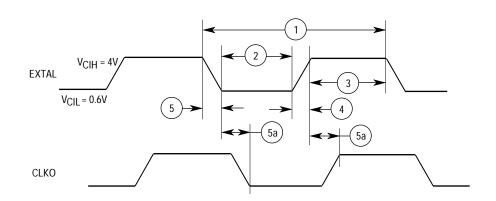

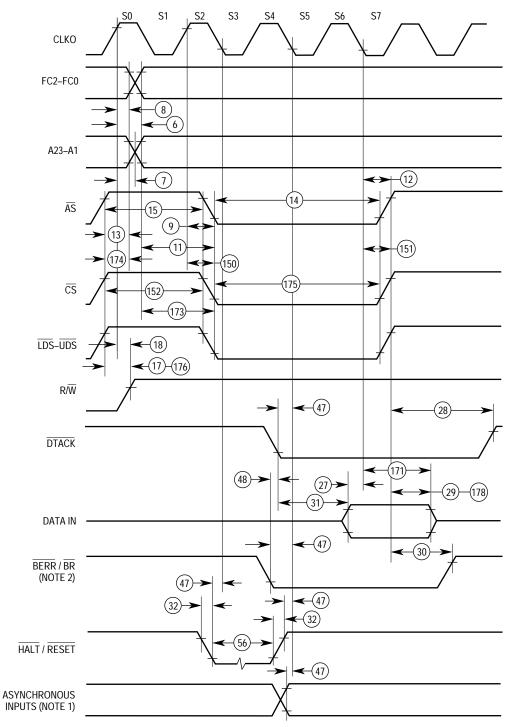

| 3.7                 | On-Chip Clock Generator                           | 3-49           |

| 3.8                 | System Control                                    | 3-50           |

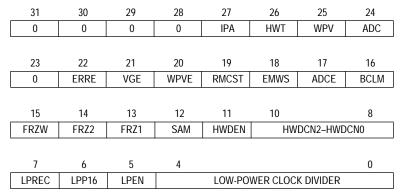

| 3.8.1               | System Control Register (SCR)                     | 3-50           |

| 3.8.2               | System Status Bits                                |                |

| 3.8.3               | System Control Bits                               | 3-52           |

| 3.8.4               | Disable CPU Logic (M68000)                        | 3-54           |

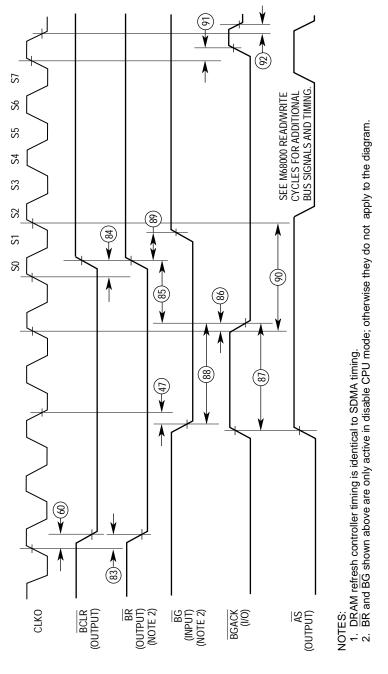

| 3.8.5               | Bus Arbitration Logic                             | 3-56           |

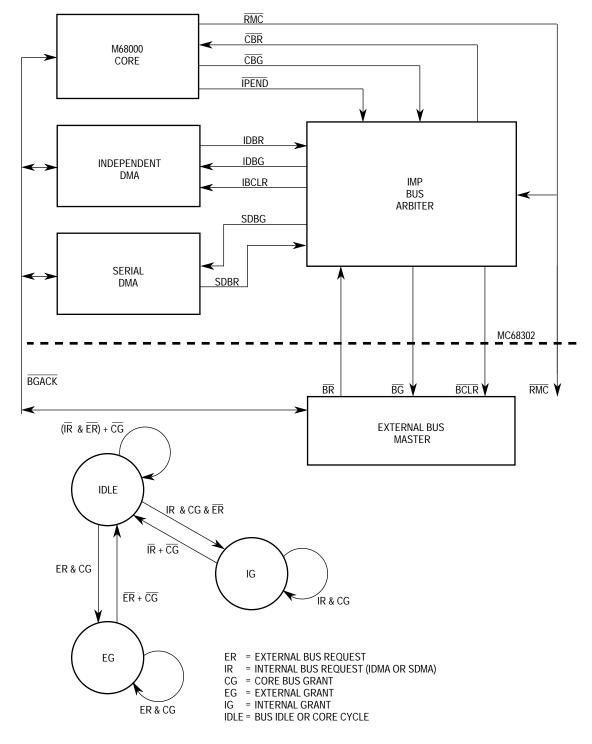

| 3.8.5.1             | Internal Bus Arbitration                          | 3-56           |

| 3.8.5.2             | External Bus Arbitration                          | 3-58           |

| 3.8.6               | Hardware Watchdog                                 |                |

| 3.8.7               | Reducing Power Consumption                        | 3-60           |

| 3.8.7.1             | Power-Saving Tips                                 | 3-60           |

| 3.8.7.2             | Low-Power (Standby) Modes                         | 3-60           |

| 3.8.7.2.1           | Low-Power Mode                                    | 3-61           |

| 3.8.7.2.2           | Lowest Power Mode                                 | 3-62           |

| 3.8.7.2.3           | Lowest Power Mode with External Clock             | 3-62           |

| 3.9                 | Clock Control Register                            |                |

| 3.9.1               | Freeze Control                                    | 3-65           |

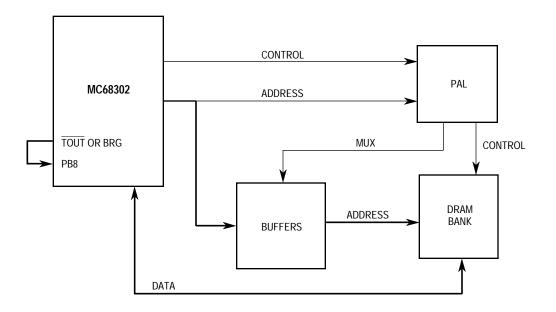

| 3.10                | Dynamic Ram Refresh Controller                    | 3-66           |

| 3.10.1              | Hardware Setup                                    |                |

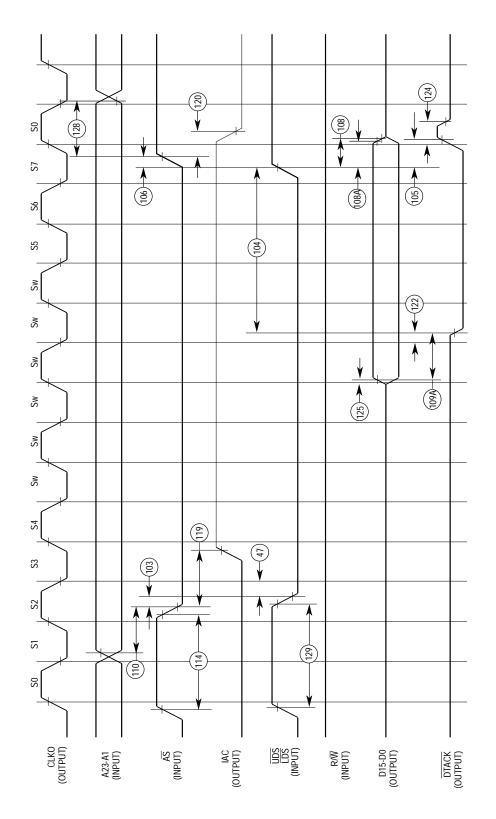

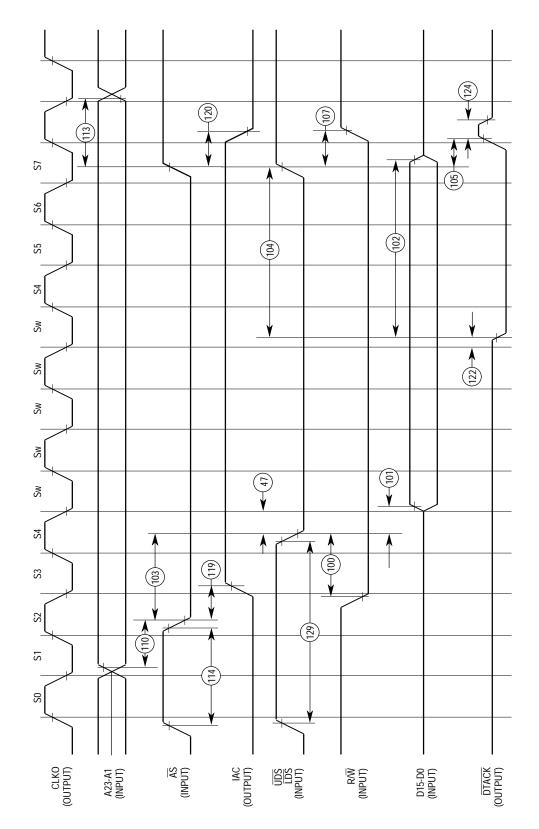

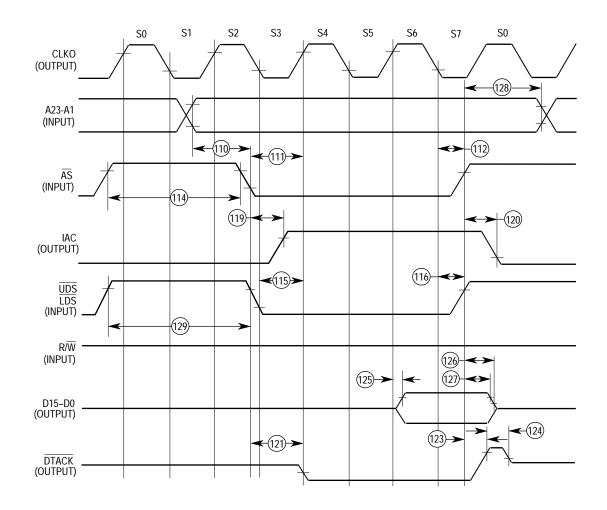

| 3.10.2              | DRAM Refresh Controller Bus Timing                |                |

| 3.10.3              | Refresh Request Calculations                      |                |

| 3.10.4              | Initialization                                    |                |

| 3.10.5              | DRAM Refresh Memory Map                           |                |

| 3.10.6              | Programming Example                               | 3-69           |

#### Section 4 **Communications Processor (CP)**

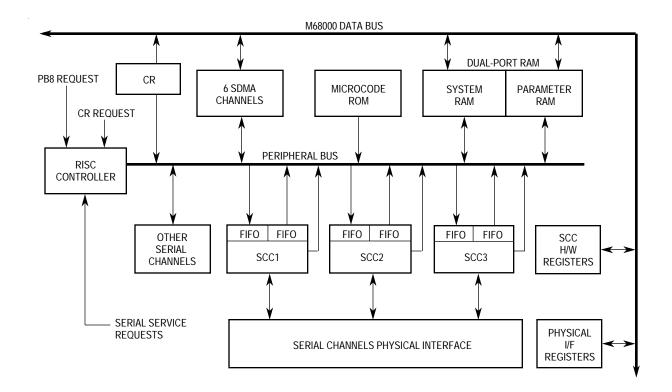

| 4.1   | Main Controller                        | 4-1  |

|-------|----------------------------------------|------|

| 4.2   | SDMA Channels                          | 4-3  |

| 4.3   | Command Set                            | 4-5  |

| 4.3.1 | Command Execution Latency              | 4-7  |

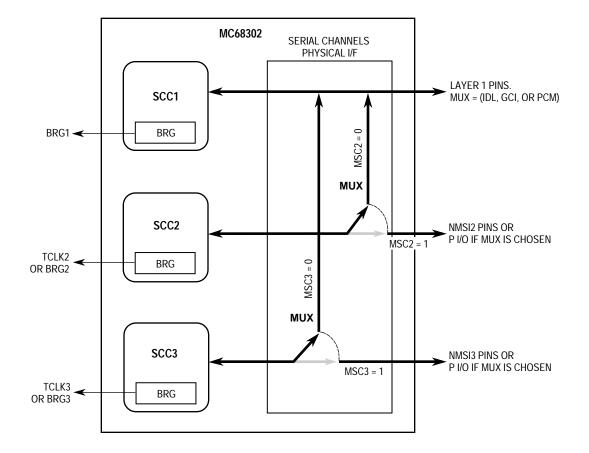

| 4.4   | Serial Channels Physical Interface     | 4-7  |

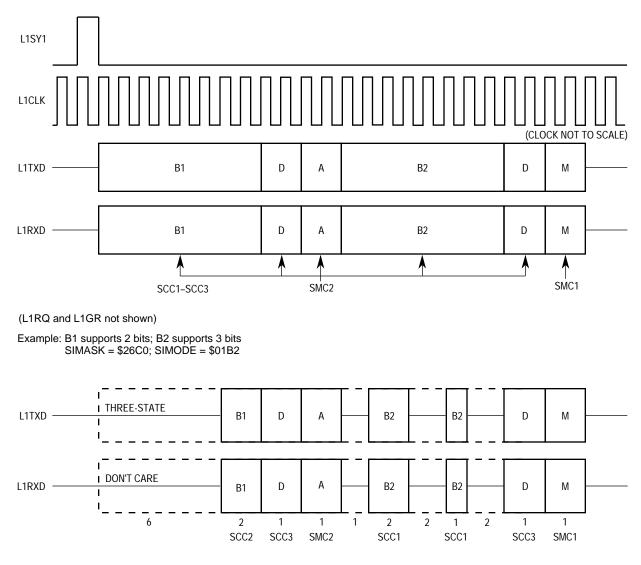

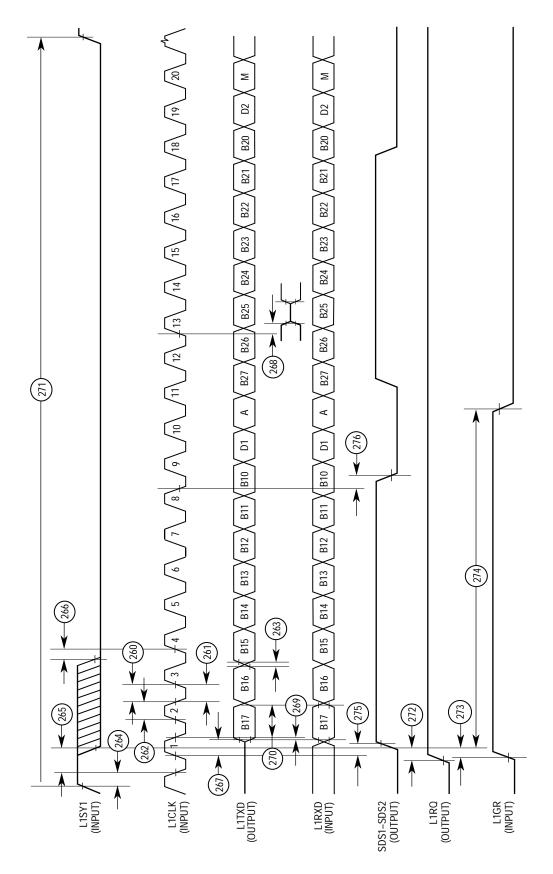

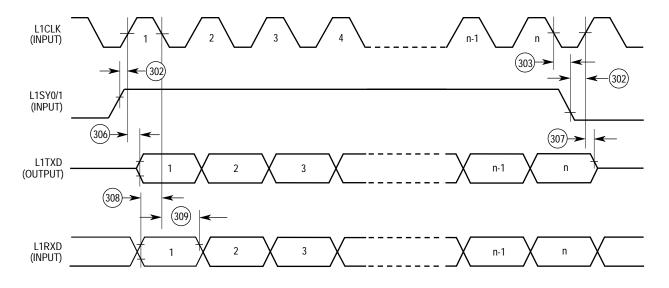

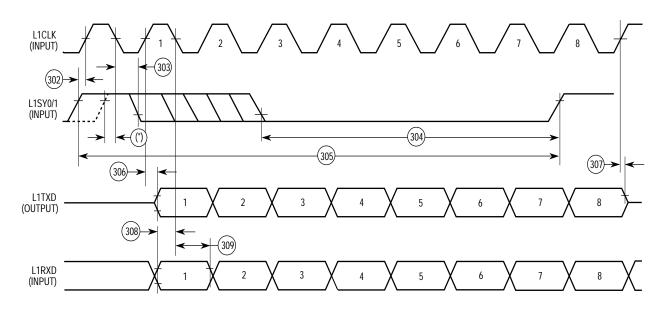

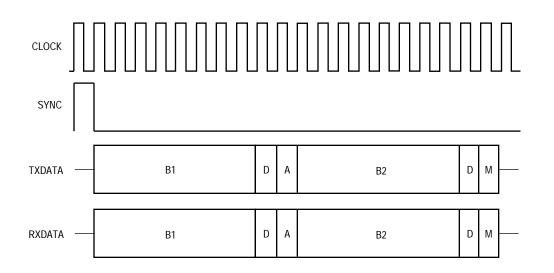

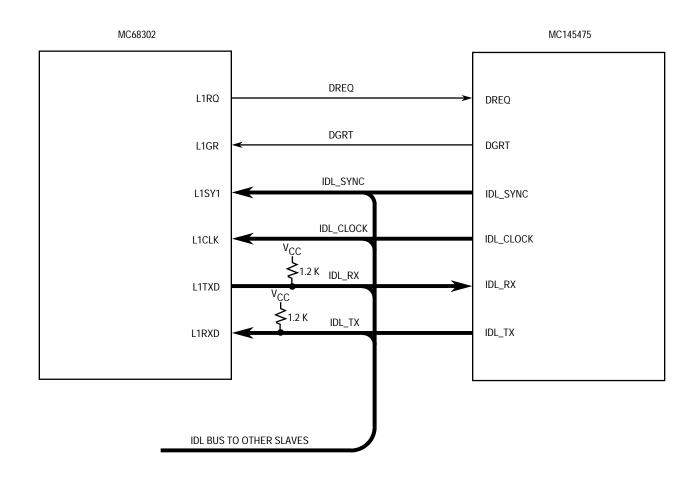

| 4.4.1 | IDL Interface                          |      |

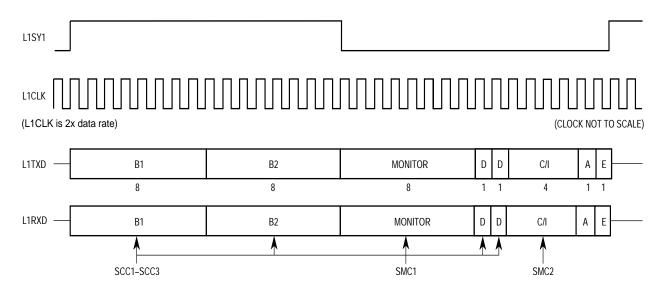

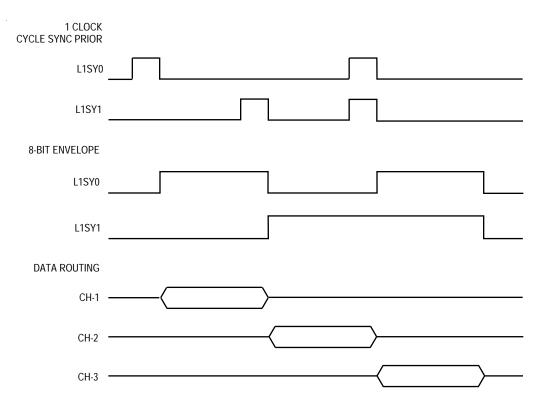

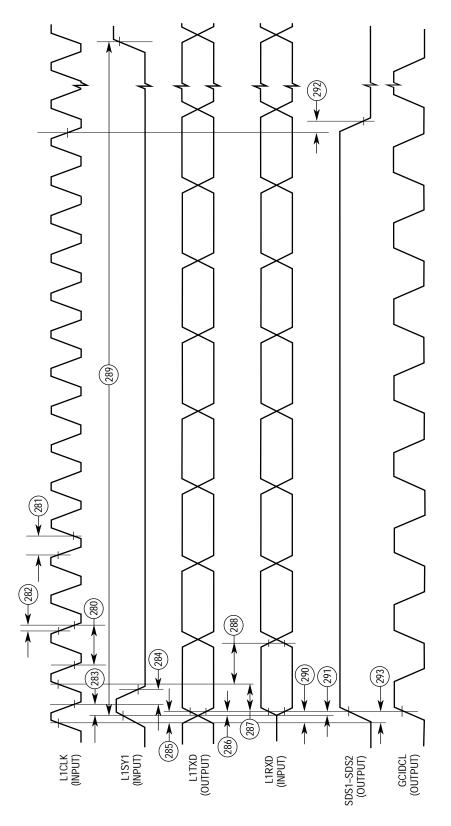

| 4.4.2 | GCI Interface                          | 4-14 |

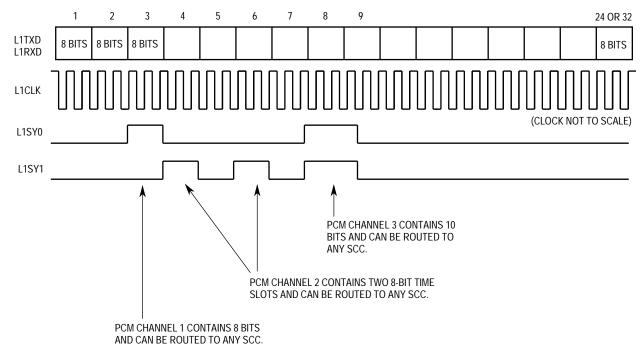

| 4.4.3 | PCM Highway Mode                       | 4-16 |

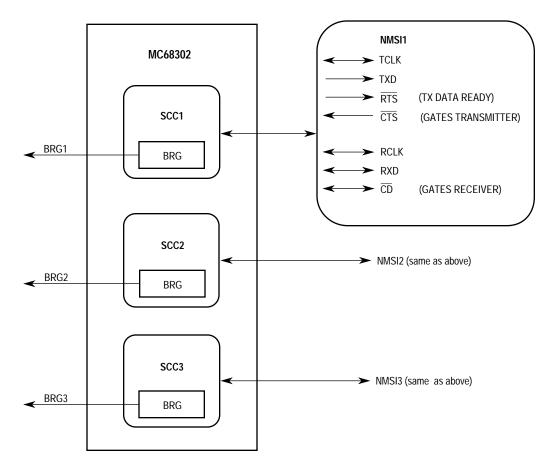

| 4.4.4 | Nonmultiplexed Serial Interface (NMSI) | 4-19 |

| Paragraph<br>Number  | Title                                           | Page<br>Number |

|----------------------|-------------------------------------------------|----------------|

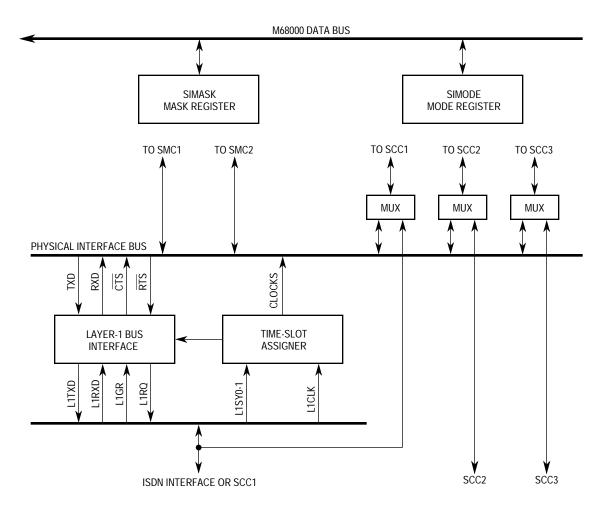

| 4.4.5                | Serial Interface Registers                      | 4-19           |

| 4.4.5.1              | Serial Interface Mode Register (SIMODE)         |                |

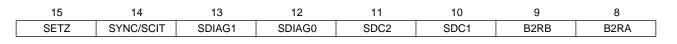

| 4.4.5.2              | Serial Interface Mask Register (SIMASK)         | 4-22           |

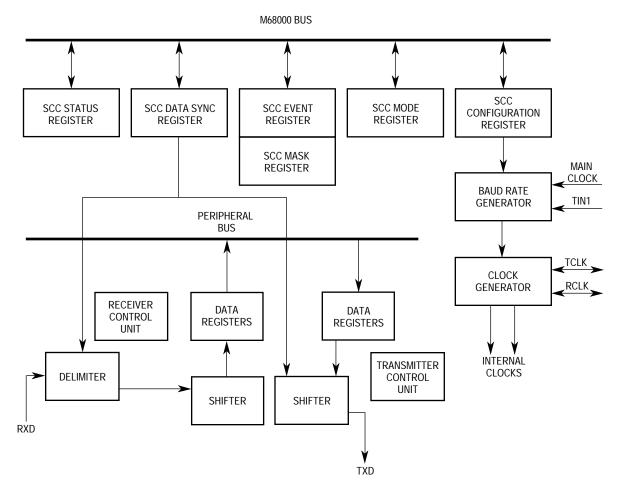

| 4.5                  | Serial Communication Controllers (SCCs)         | 4-22           |

| 4.5.1                | SCC Features                                    |                |

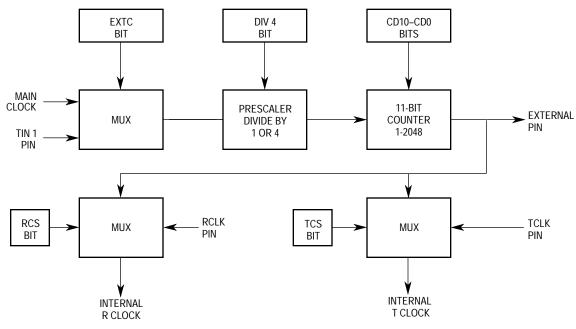

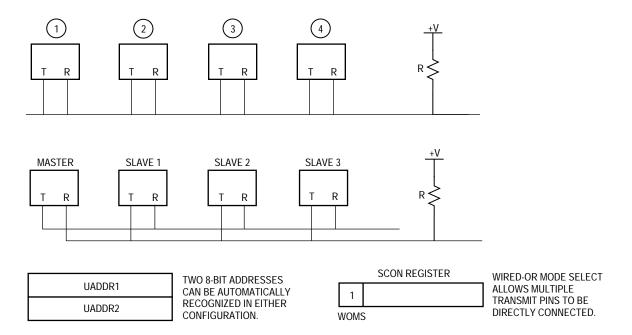

| 4.5.2                | SCC Configuration Register (SCON)               |                |

| 4.5.2.1              | Asynchronous Baud Rate Generator Examples       |                |

| 4.5.2.2              | Synchronous Baud Rate Generator Examples        |                |

| 4.5.3                | SCC Mode Register (SCM)                         |                |

| 4.5.4                | SCC Data Synchronization Register (DSR)         |                |

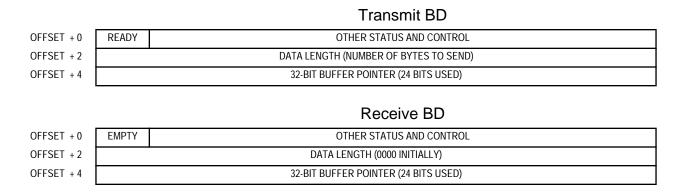

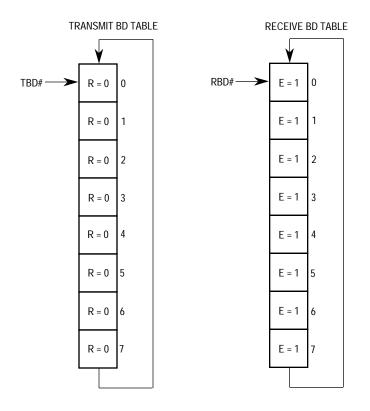

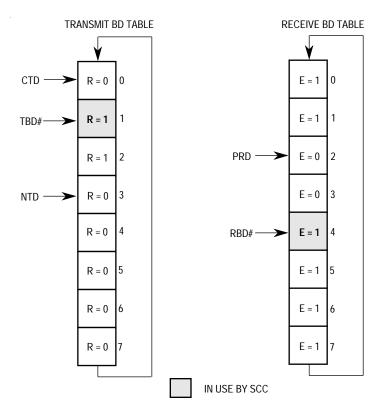

| 4.5.5                | Buffer Descriptors Table                        |                |

| 4.5.6                | SCC Parameter RAM Memory Map                    |                |

| 4.5.6.1              | Data Buffer Function Code Register (TFCR, RFCR) |                |

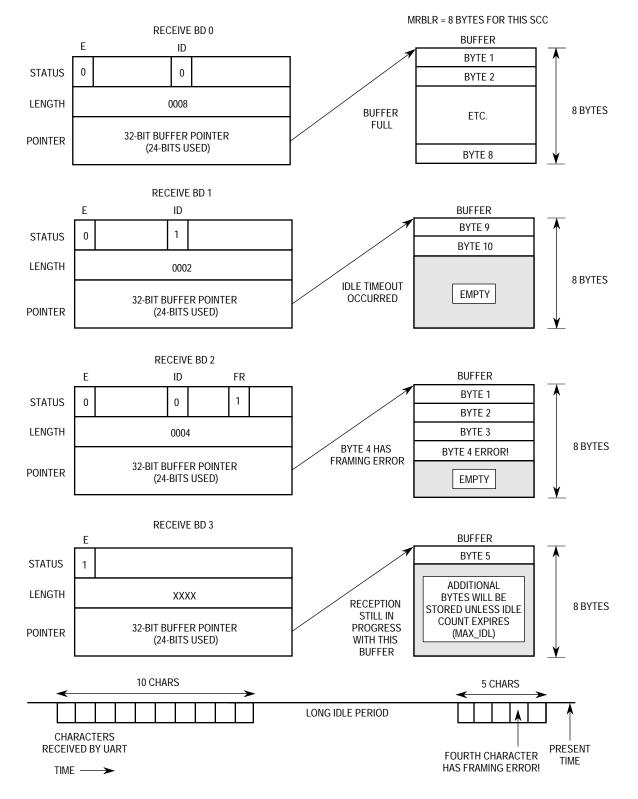

| 4.5.6.2              | Maximum Receive Buffer Length Register (MRBLR)  |                |

| 4.5.6.3              | Receiver Buffer Descriptor Number (RBD#)        |                |

| 4.5.6.4              | Transmit Buffer Descriptor Number (TBD#)        |                |

| 4.5.6.5              | Other General Parameters                        |                |

| 4.5.7                | SCC Initialization                              |                |

| 4.5.8                | Interrupt Mechanism                             |                |

| 4.5.8.1              | SCC Event Register (SCCE)                       |                |

| 4.5.8.2              | SCC Mask Register (SCCM)                        |                |

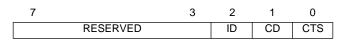

| 4.5.8.3              | SCC Status Register (SCCs)                      |                |

| 4.5.8.4              | Bus Error on SDMA Access                        |                |

| 4.5.9                | SCC Transparent Mode                            |                |

| 4.5.10               | Disabling the SCCs                              |                |

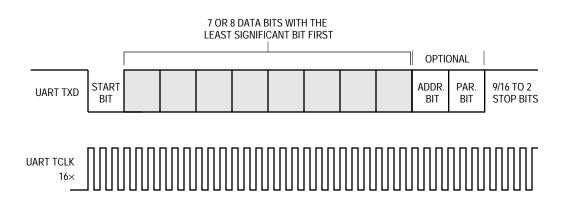

| 4.5.11               | UART Controller                                 |                |

| 4.5.11.1<br>4.5.11.2 | Normal Asynchronous Mode                        |                |

| 4.5.11.2             | Asynchronous DDCMP MODE                         |                |

| 4.5.11.3             | UART Memory Map<br>UART Programming Model       |                |

| 4.5.11.4             | UART Command Set                                |                |

| 4.5.11.6             | UART Address Recognition                        |                |

| 4.5.11.7             | UART Control Characters and Flow Control        |                |

| 4.5.11.8             | Send Break                                      |                |

| 4.5.11.9             | Send Preamble (IDLE)                            |                |

| 4.5.11.10            | Wakeup Timer                                    |                |

| 4.5.11.11            | UART Error-Handling Procedure                   |                |

| 4.5.11.12            | Fractional Stop Bits                            |                |

| 4.5.11.13            | UART Mode Register.                             |                |

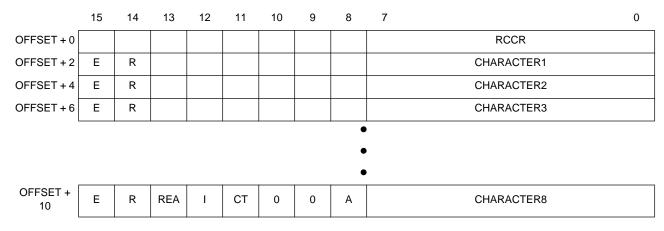

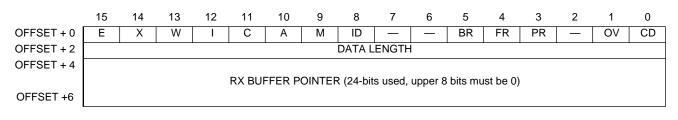

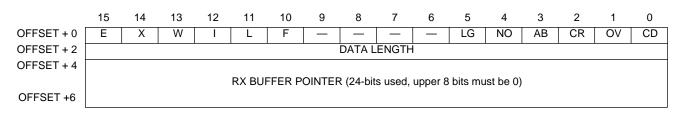

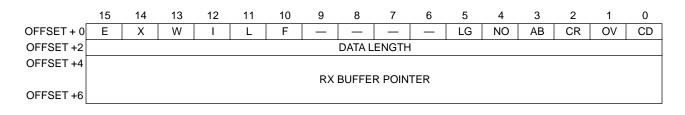

| 4.5.11.14            | UART Receive Buffer Descriptor (Rx BD)          |                |

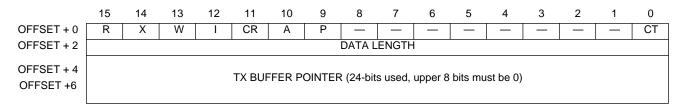

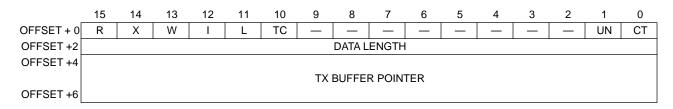

| 4.5.11.15            | UART Transmit Buffer Descriptor (Tx BD)         |                |

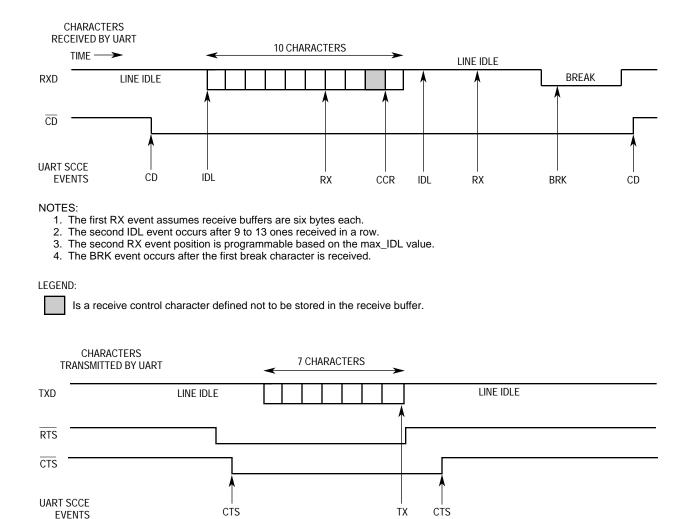

| 4.5.11.16            | UART Event Register                             |                |

| 4.5.11.17            | UART MASK Register                              |                |

| 4.5.11.18            | S-Records Programming Example                   |                |

| 4.5.12               | HDLC Controller                                 |                |

| Paragraph<br>Number | Title                                                           | Page<br>Number |

|---------------------|-----------------------------------------------------------------|----------------|

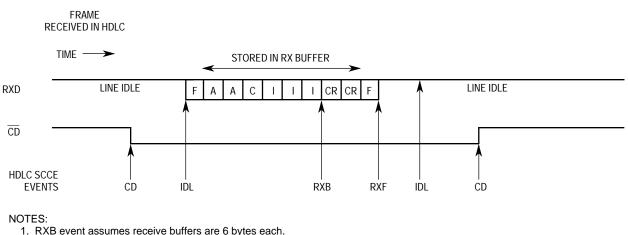

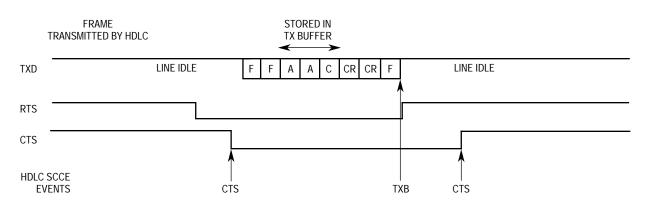

| 4.5.12.1            | HDLC Channel Frame Transmission Processing                      | 4-68           |

| 4.5.12.2            | HDLC Channel Frame Reception Processing                         | 4-68           |

| 4.5.12.3            | HDLC Memory Map                                                 | 4-69           |

| 4.5.12.4            | HDLC Programming Model                                          | 4-69           |

| 4.5.12.5            | HDLC Command Set                                                |                |

| 4.5.12.6            | HDLC Address Recognition                                        | 4-71           |

| 4.5.12.7            | HDLC Maximum Frame Length Register (MFLR)                       | 4-71           |

| 4.5.12.8            | HDLC Error-Handling Procedure                                   | 4-72           |

| 4.5.12.9            | HDLC Mode Register                                              |                |

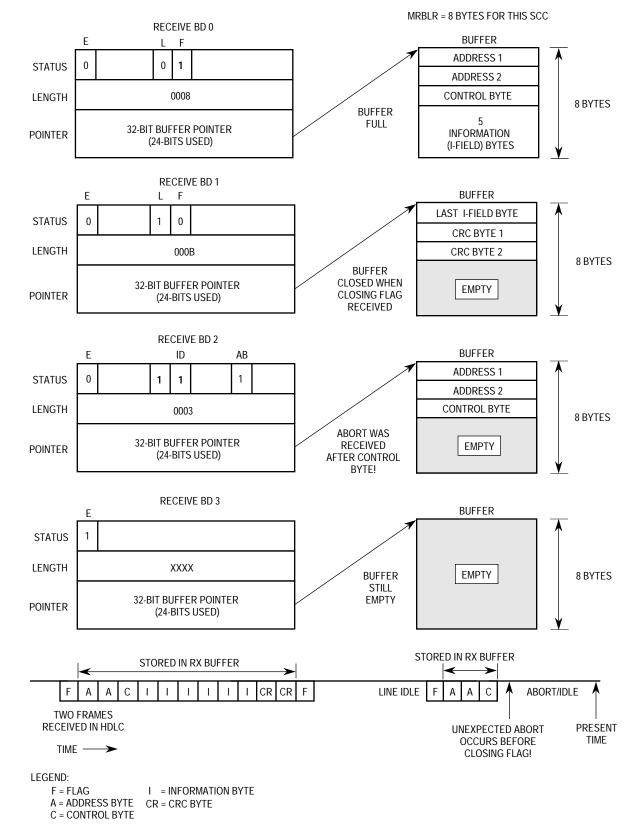

| 4.5.12.10           | HDLC Receive Buffer Descriptor (Rx BD)                          |                |

| 4.5.12.11           | HDLC Transmit Buffer Descriptor (Tx BD)                         |                |

| 4.5.12.12           | HDLC Event Register                                             |                |

| 4.5.12.13           | HDLC Mask Register                                              |                |

| 4.5.13              | BISYNC Controller                                               |                |

| 4.5.13.1            | Bisync Channel frame Transmission Processing                    |                |

| 4.5.13.2            | Bisync Channel Frame Reception Processing                       |                |

| 4.5.13.3            | Bisync Memory Map                                               |                |

| 4.5.13.4            | BISYNC Command Set                                              |                |

| 4.5.13.5            | BISYNC Control Character Recognition                            |                |

| 4.5.13.6            | BSYNC-BISYNC SYNC Register                                      |                |

| 4.5.13.7            | BDLE-BISYNC DLE Register                                        |                |

| 4.5.13.8            | BISYNC Error-Handling Procedure                                 |                |

| 4.5.13.9            | BISYNC Mode Register                                            |                |

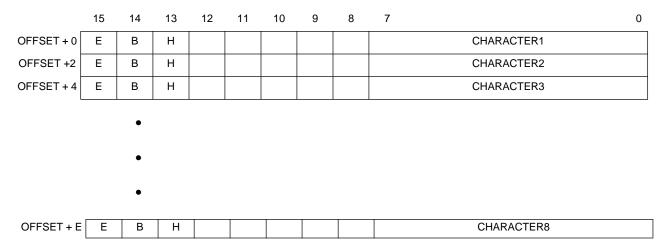

| 4.5.13.10           | BISYNC Receive Buffer Descriptor (Rx BD)                        |                |

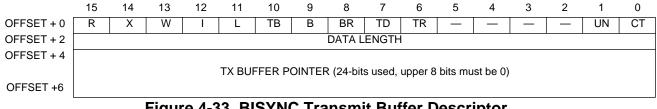

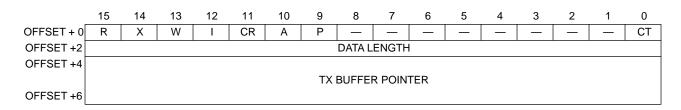

| 4.5.13.11           | BISYNC Transmit Buffer Descriptor (Tx BD)                       |                |

| 4.5.13.12           | BISYNC Event Register                                           |                |

| 4.5.13.13           | BISYNC Mask Register                                            |                |

| 4.5.13.14<br>4.5.14 | Programming the BISYNC Controllers<br>DDCMP Controller          |                |

| 4.5.14              | DDCMP Controller<br>DDCMP Channel Frame Transmission Processing |                |

| 4.5.14.1            | DDCMP Channel Frame Reception Processing.                       |                |

| 4.5.14.3            | DDCMP Channel Frame Reception Frocessing.                       |                |

| 4.5.14.4            | DDCMP Programming Model                                         |                |

| 4.5.14.5            | DDCMP Command Set.                                              |                |

| 4.5.14.6            | DDCMP Control Character Recognition                             |                |

| 4.5.14.7            | DDCMP Address Recognition                                       |                |

| 4.5.14.8            | DDCMP Error-Handling Procedure                                  |                |

| 4.5.14.9            | DDCMP Mode Register                                             |                |

| 4.5.14.10           | DDCMP Receive Buffer Descriptor (Rx BD)                         |                |

| 4.5.14.11           | DDCMP Transmit Buffer Descriptor (Tx BD)                        |                |

| 4.5.14.12           | DDCMP Event Register                                            |                |

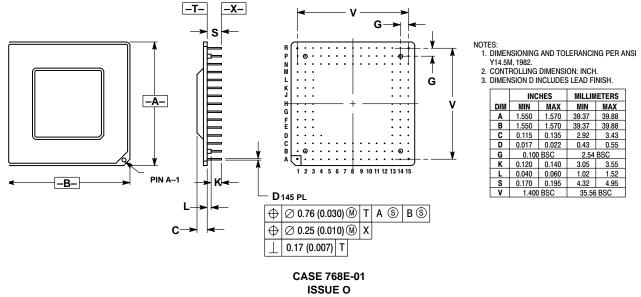

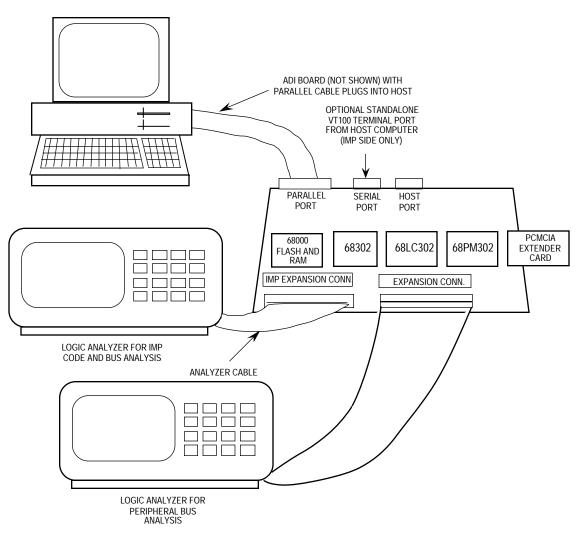

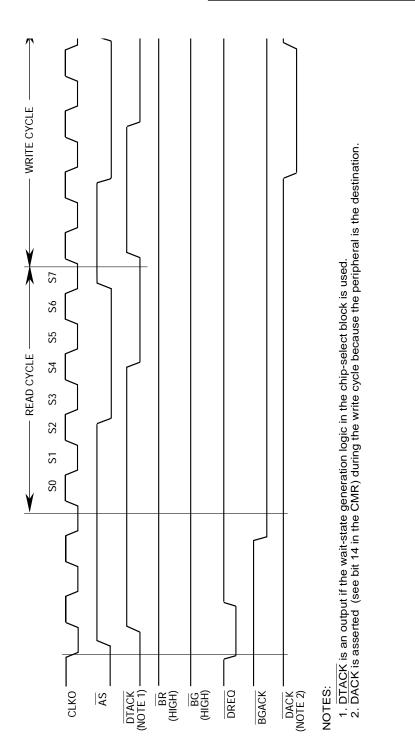

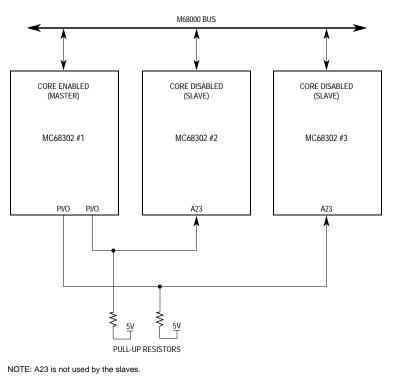

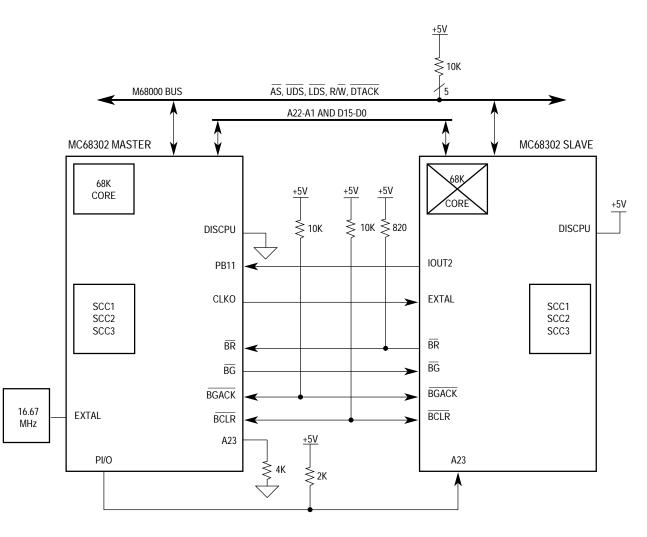

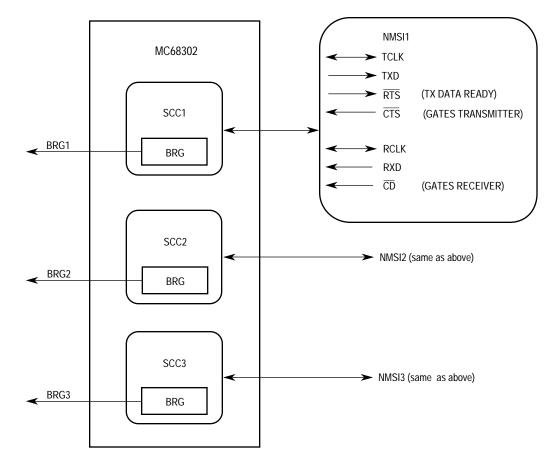

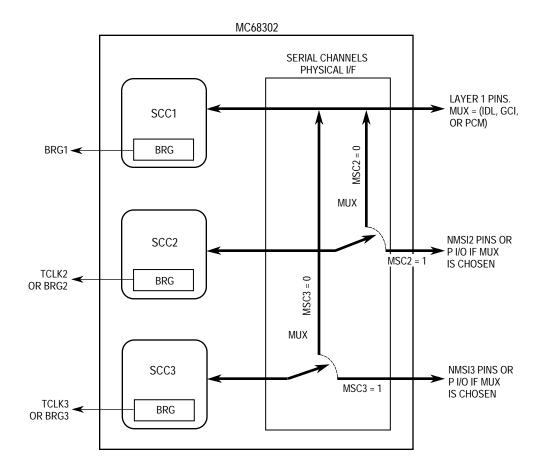

| 4.5.14.13           | DDCMP Mask Register                                             |                |